Decoder is a combinational circuit that has ‘n‘ input lines and maximum of 2n output lines. One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. It means that Decoder detect a particular code. The output of the decoder are nothing but the min terms of ‘n‘ input variables (lines), when it is enabled.

A decoder is a combinational circuit which has many inputs and many outputs. It is used to convert binary data to other codes. Examples: binary to octal conversion using 3 to 8 decoder, BCD to decimal conversion using 4 to 10 decoder, binary to hexadecimal conversion using 4 to 16 decoder, etc.

→ 2 to 4 decoder is the minimum possible decoder.

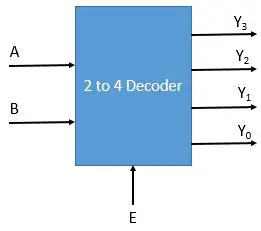

2 to 4 Decoder

Let 2 to 4 decoder has two inputs A and B and four outputs Y3, Y2, Y1, and Y0. The block diagram of 2 to 4 decoder is shown in the following figure.

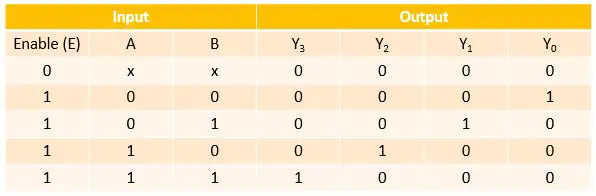

One of these four outputs will be ‘1’ for each combination of inputs when enable E is ‘1’. The truth table of 2 to 4 decoder is shown below.

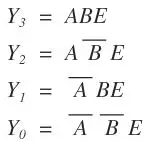

From truth table, we can write the Boolean functions (logical expressions) for each output as

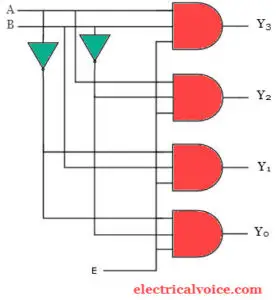

Each output is having one product term. So, there are four product terms in total. We can implement these four product terms by using four AND gates having three inputs each and two inverters. The circuit diagram of 2 to 4 decoder is shown in the following figure.

Therefore, the outputs of 2 to 4 decoder are nothing but the min terms of two input variables A and B when enable E is equal to 1. If enable E is zero, then all the outputs of the decoder will be equal to zero.

Note:

1. The internal circuitry of decoder and demux are exactly same.

2. A decoder with enable input can function as a demultiplexer.

3. A 2 × 4 line decoder may acts like a 1:4 demux and vice-versa.

4. Decoder contains AND gates or NAND gates.

Decoder Applications

1. Decoders are used to input data to a specified output line as is done in addressing core memory where input data is to be stored in a specified memory location.

2. It is used in code conversions.

3. In high-performance memory systems, this decoder can be used to minimize the effects of system decoding.

4. It may also be used for data distribution i.e. demultiplexing.

5. Decoder is designed to be used in high-performance memory-decoding or data-routing applications requiring very short propagation delay times.

6. Decoders can be used as timing or sequencing signals to turn devices on or off at specific times, because when the decoder inputs come from a counter that is being continually pulsed, the decoder outputs will be activated sequentially.